ADC0808中文资料

典型的集成ADC芯片

为了满足多种需要,目前国内外各半导体器件生产厂家设计并生产出了多种多样的ADC芯片。仅美国AD公司的ADC产品就有几十个系列、近百种型号之多。从性能上讲,它们有的精度高、速度快,有的则价格低廉。从功能上讲,有的不仅具有A/D转换的基本功能,还包括内部放大器和三态输出锁存器;有的甚至还包括多路开关、采样保持器等,已发展为一个单片的小型数据采集系统。

尽管ADC芯片的品种、型号很多,其内部功能强弱、转换速度快慢、转换精度高低有很大差别,但从用户最关心的外特性看,无论哪种芯片,都必不可少地要包括以下四种基本信号引脚端:模拟信号输入端(单极性或双极性);数字量输出端(并行或串行);转换启动信号输入端;转换结束信号输出端。除此之外,各种不同型号的芯片可能还会有一些其他各不相同的控制信号端。选用ADC芯片时,除了必须考虑各种技术要求外,通常还需了解芯片以下两方面的特性。

(1)数字输出的方式是否有可控三态输出。有可控三态输出的ADC芯片允许输出线与微机系统的数据总线直接相连,

并在转换结束后利用读数信号RD选通三态门,将转换结果送上总线。没有可控三态输出(包括内部根本没有输出三态门和虽有三态门、但外部不可控两种情况)的ADC芯片则不允许数据输出线与系统的数据总线直接相连,而必须通过I/O接口与MPU交换信息。

(2)启动转换的控制方式是脉冲控制式还是电平控制式。对脉冲启动转换的ADC芯片,只要在其启动转换引脚上施加一个宽度符合芯片要求的脉冲信号,就能启动转换并自动完成。一般能和MPU配套使用的芯片,MPU的I/O写脉冲都能满足ADC芯片对启动脉冲的要求。对电平启动转换的ADC芯片,在转换过程中启动信号必须保持规定的电平不变,否则,如中途撤消规定的电平,就会停止转换而可能得到错误的结果。为此,必须用D触发器或可编程并行I/O接口芯片的某一位来锁存这个电平,或用单稳等电路来对启动信号进行定时变换。

具有上述两种数字输出方式和两种启动转换控制方式的ADC芯片都不少,在实际使用芯片时要特别注意看清芯片说明。下面介绍两种常用芯片的性能和使用方法。

1. ADC 0808/0809

ADC 0808和ADC 0809除精度略有差别外(前者精度为8位、后者精度为7位),其余各方面完全相同。它们都是CMOS器件,不仅包括一个8位的逐次逼近型的ADC部分,而且还提供一个8通道的模拟多路开关和通道寻址逻辑,因而有理由把它作为简单的“数据采集系统”。利用它可直接输入8个单端的模拟信号分时进行A/D转换,在多点巡回检测和过程控制、运动控制中应用十分广泛。

1) 主要技术指标和特性

(1)分辨率: 8位。

(2)总的不可调误差: ADC0808

为±21 LSB,ADC 0809为±1LSB。

(3)转换时间: 取决于芯片时钟频率,如CLK=500kHz时,TCONV=128μs。

(4)单一电源: +5V。

(5)模拟输入电压范围: 单极性0~5V;双极性±5V,±10V(需外加一定电路)。

(6)具有可控三态输出缓存器。

(7)启动转换控制为脉冲式(正脉冲),上升沿使所有内部寄存器清零,下降沿使A/D转换开始。

(8)使用时不需进行零点和满刻度调节。

2) 内部结构和外部引脚

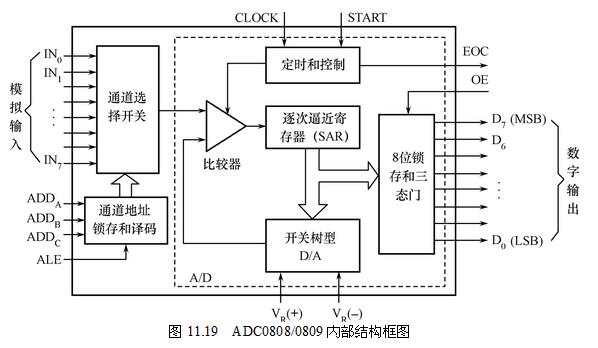

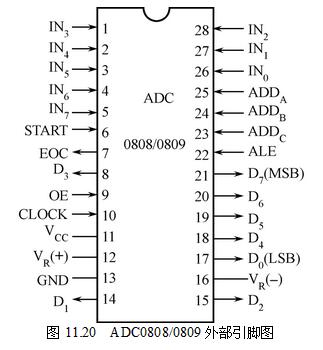

ADC0808/0809的内部结构和外部引脚分别如图11.19和图11.20所示。内部各部分的作用和工作原理在内部结构图中已一目了然,在此就不再赘述,下面仅对各引脚定义分述如下:

(1)IN0~IN7——8路模拟输入,通过3根地址译码线ADDA、ADDB、ADDC来选通一路。

(2)D7~D0——A/D转换后的数据输出端,为三态可控输出,故可直接和微处理器数据线连接。8位排列顺序是D7为最高位,D0为最低位。

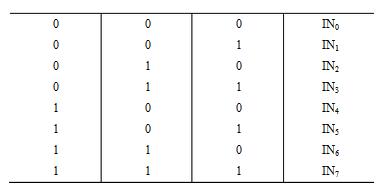

(3)ADDA、ADDB、ADDC——模拟通道选择地址信号,ADDA为低位,ADDC为高位。地址信号与选中通道对应关系如表11.3所示。

(4)VR(+)、VR(-)——正、负参考电压输入端,用于提供片内DAC电阻网络的基准电压。在单极性输入时,VR(+)=5V,VR(-)=0V;双极性输入时,VR(+)、VR(-)分别接正、负极性的参考电压。

(5)ALE——地址锁存允许信号,高电平有效。当此信号有效时,A、B、C三位地址信号被锁存,译码选通对应模拟通道。在使用时,该信号常和START信号连在一起,以便同时锁存通道地址和启动A/D转换。

(6)START——A/D转换启动信号,正脉冲有效。加于该端的脉冲的上升沿使逐次逼近寄存器清零,下降沿开始A/D转换。如正在进行转换时又接到新的启动脉冲,则原来的转换进程被中止,重新从头开始转换。

(7)EOC——转换结束信号,高电平有效。该信号在A/D转换过程中为低电平,其余时间为高电平。该信号可作为被CPU查询的状态信号,也可作为对CPU的中断请求信号。在需要对某个模拟量不断采样、转换的情况下,EOC也可作为启动信号反馈接到START端,但在刚加电时需由外电路第一次启动。

(8)OE——输出允许信号,高电平有效。当微处理器送出该信号时,ADC0808/0809的输出三态门被打开,使转换结果通过数据总线被读走。在中断工作方式下,该信号往往是CPU发出的中断请求响应信号。

3) 工作时序与使用说明

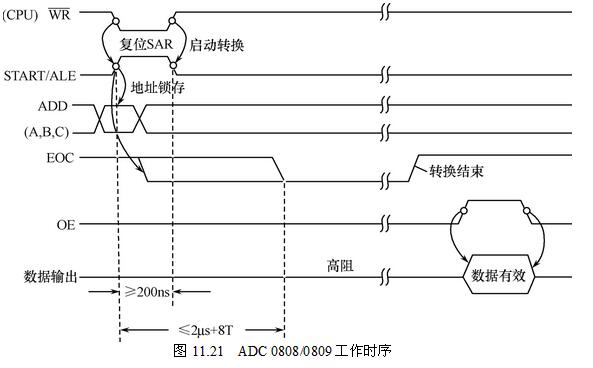

ADC 0808/0809的工作时序如图11.21所示。当通道选择地址有效时,ALE信号一出现,地址便马上被锁存,这时转换启动信号紧随ALE之后(或与ALE同时)出现。START的上升沿将逐次逼近寄存器SAR复位,在该上升沿之后的2μs加8个时钟周期内(不定),EOC信号将变低电平,以指示转换操作正在进行中,直到转换完成后EOC再变高电平。微处理器收到变为高电平的EOC信号后,便立即送出OE信号,打开三态门,读取转换结果。

| 赞() |