**TOSHIBA** TC9285P

#### TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# TC9285P

## INFRARED REMOTE CONTROL RECEIVING LSI

The TC9285P is an infrared Remote Control signal receiving LSI is suited for remote control of audio system, TV, VTR, CD player, etc.

In combination with the transmission LSI: TC9243P, TC9243F, a remote control system can be easily composed.

- Basic functions: 11 functions Hold pulse: 9 functions Cyclic pulse: 2 functions

- 3 functions out of 7 hold pulse functions are shift key outputs and can be output in parallel with other outputs corresponding to double-pushed signals sent from sending side.

• 8bit system codes are detected. System codes permitting signal receiving can be set up to 4 bits. Interference with other equipment can be thus prevented.

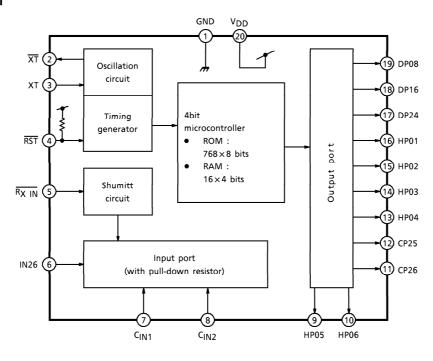

#### PIN CONNECTION

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

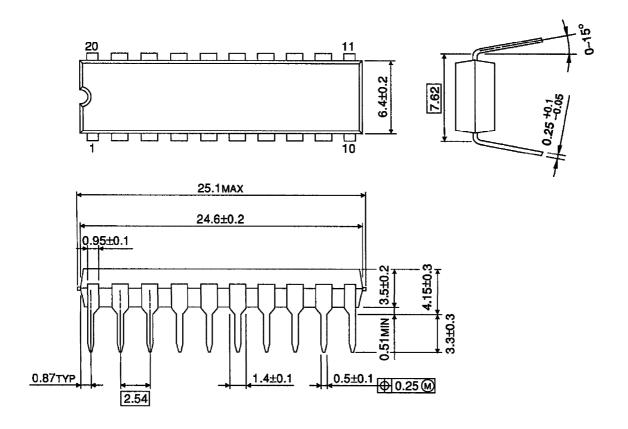

DIP20-P-300-2.54A

Weight: 1.4g (Typ.)

#### **BLOCK DIAGRAM**

# **PIN FUNCTION**

| PIN No.                 | SYMBOL                              | PIN NAME                    | FUNCTION & OPERATION                                                                                                                            |                  |  |  |  |  |  |  |

|-------------------------|-------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|--|--|--|--|--|

| 20                      | GND<br>V <sub>DD</sub>              | Power supply terminal       | Applies supply voltage. $(V_{DD} = 5.0V \text{ Typ.})$                                                                                          |                  |  |  |  |  |  |  |

| 2                       | XT                                  | Oscillator                  | Input/output terminals for the ceramic o                                                                                                        | scillators, with |  |  |  |  |  |  |

| 3                       | XT                                  | terminal                    | built-in amplifier circuit and feedback res                                                                                                     | istor.           |  |  |  |  |  |  |

| 4                       | RST                                 | Reset input                 | Reset input When this pin is set at "L" level, the inside is in With a pull-up resistor.                                                        |                  |  |  |  |  |  |  |

| 5                       | R <sub>X IN</sub>                   | Remote control signal input |                                                                                                                                                 |                  |  |  |  |  |  |  |

| 6                       | IN26                                | Cyclic input                | ut  Every time "H" is input, CP26 output is reversed.  With a pull-down resistor.                                                               |                  |  |  |  |  |  |  |

| 7, 8                    | C <sub>IN1</sub> , C <sub>IN2</sub> | Code input                  | Input terminal to set system code permitt                                                                                                       | ing receiving.   |  |  |  |  |  |  |

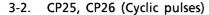

| 11, 12                  | CP26, CP25                          | Cyclic output               | Every time corresponding remote control signal is input, output is reversed. When the power source is ON (RESET), this pin is set at "L" level. | UT FORM          |  |  |  |  |  |  |

| 9, 10<br>13~16<br>17~19 | HP01~HP06<br>DP08, 16, 24           | Hold output                 | This pin is kept at "H" level as long as remote control signal is being input.                                                                  | TUATUO           |  |  |  |  |  |  |

#### **DESCRIPTION OF OPERATION**

#### 1. Establishment of system code permitting receiving

8bit system code is provided for the transmission format of the transmission LSI: TC9243P, TC9243F to prevent interference with other equipment. When this system code is established for each of various equipment, it is possible to identify equipment and prevent interference.

On the TC9285P, the lower 4 bits of a system code permitting receiving of remote control signal can be set and the upper 4 bits have been fixed at "100000". (Settable range: "80"~"83" HEX) Once a system code permitting receiving has been set up, only when the system code for the received remote control signal is in accord with the set system code, the following key data code is accepted.

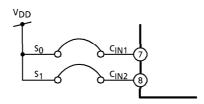

A system code permitting receiving is set by the jumpers provided between  $C_{IN1\sim2}$  pins and  $V_{DD}$ . Each of the jumpers corresponds to bit  $0\sim1$  ( $S_0\sim S_1$ ) of a system code and when the jumper is connected, the corresponding bit is set at "1".

#### 2. Check of receiving signals

A check code is provided in a single transmission waveform of the transmission format of the transmission LSI: TC9243P, TC9243F to prevent malfunction due to erroneous data take-in. A system code is followed by a forward code and a key data code is followed by a reverse code.

| LEADER PULSE |                |                | \$Y            | STEN           | /I CC      | DDE            |                |                |                |                | SYS            | TEN | / CC           | DE             |                |                |                |                | KEY            | DAT | ΓΑ C | ODE            | =              |                |                  | ŀ                | ΚEΥ            | DA         | ГА С           | ODE            |                |    |

|--------------|----------------|----------------|----------------|----------------|------------|----------------|----------------|----------------|----------------|----------------|----------------|-----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----|------|----------------|----------------|----------------|------------------|------------------|----------------|------------|----------------|----------------|----------------|----|

|              | s <sub>0</sub> | s <sub>1</sub> | S <sub>2</sub> | s <sub>3</sub> | <b>S</b> 4 | S <sub>5</sub> | s <sub>6</sub> | S <sub>7</sub> | s <sub>0</sub> | s <sub>1</sub> | s <sub>2</sub> | \$3 | S <sub>4</sub> | S <sub>5</sub> | s <sub>6</sub> | S <sub>7</sub> | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D3  | D4   | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> | $\overline{D_0}$ | $\overline{D_1}$ | D <sub>2</sub> | <u>D</u> 3 | D <sub>4</sub> | D <sub>5</sub> | D <sub>6</sub> | D7 |

The TC9285P fully decodes all data and regards the data valid only when the first and second codes sent twice agree with each other.

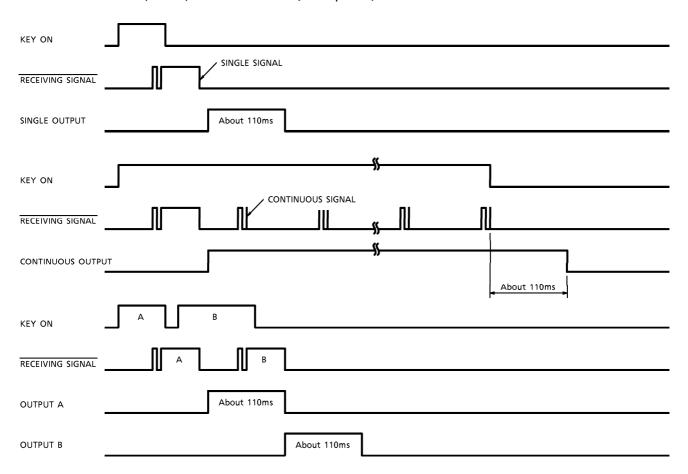

- 3. Output pulses HP, DP and CP

- 3-1. HP01~HP06, DP08, DP16 and DP24 (Hold pulses)

The hold pulse checks a system code of an initial single signal and a received signal and becomes "H" level only when data is valid.

If a received signal is single signal, the output becomes "L" level about 110ms later.

The output is held at "H" level as long as the key is kept pushed continuously after a single signal was output and continuous signals are being input.

If the key was released and the continuous signals have been stopped, it is judged that the key was released about 110ms later from the last continuous signal and the output is set at "L" level.

Further, DP08, DP16 and DP24 are shift key outputs and can be set at "H" level in parallel with other outputs corresponding to the double pushed signals sent from a transmitter.

The output of this LSI is best suited for REC-PLAY, REC-PAUSE and REC-REV outputs of a tape deck.

- The cyclic pulse is reversed every time a single signal is received.

Further, CP26 can be reversed by setting the IN26 pin at "H" level.

Because this input is not valid unless output is stabilized for 4ms, no external part for preventing chattering is required.

- This cyclic pulse is best suited for outputs of power supply ON/OFF, MUTE, etc.

- When output of HP03, HP04 or CP26 is generated, cyclic output of CP25 is cleared.

- 4. Code assignment (Key No. are transmission key No. of TC9243P, TC9243F.)

| IZENZ NI        |                |                | KE             | Y DAT          | A CO           | DE             |                |                | OLITBUIT | FUNCTION |

|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------|----------|

| KEY No.         | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> | OUTPUT   | FUNCTION |

| K <sub>01</sub> | 1              | 0              | 0              | 0              | 0              | *              | *              | *              | HP01     |          |

| K <sub>02</sub> | 0              | 1              | 0              | 0              | 0              | *              | *              | *              | HP02     |          |

| K <sub>03</sub> | 1              | 1              | 0              | 0              | 0              | *              | *              | *              | HP03     | Hold     |

| K <sub>04</sub> | <del> </del>   |                | 1              | 0              | 0              | *              | *              | *              | HP04     | поіц     |

| K <sub>05</sub> |                |                | 1              | 0              | 0              | *              | *              | *              | HP05     |          |

| K <sub>06</sub> | 0              | 1              | 1              | 0              | 0              | *              | *              | *              | HP06     |          |

| K <sub>08</sub> | *              | *              | *              | *              | *              | 1              | 0              | 0              | DP08     | Hold     |

| K <sub>16</sub> | *              | *              | *              | *              | *              | 1              | 1              | 0              | DP16     | &        |

| K <sub>24</sub> | *              | *              | *              | *              | *              | 1              | 0              | 1              | DP32     | Shift    |

| K <sub>25</sub> | 1              | 0              | 0              | 1              | 1              | *              | *              | *              | CP25     | Cyclic   |

| K <sub>26</sub> | 0              | 1              | 0              | 1              | 1              | *              | *              | *              | CP26     | Суспс    |

※ : Don't care (Corresponding outputs change regardless of data.)

# MAXIMUM RATINGS (Ta = 25°C)

| CHARACTERISTIC        | SYMBOL           | RATING                        | UNIT     |

|-----------------------|------------------|-------------------------------|----------|

| Supply Voltage        | $V_{DD}$         | -0.3~6.0                      | <b>V</b> |

| Input Voltage         | $v_{IN}$         | $GND - 0.3 \sim V_{DD} + 0.3$ | >        |

| Power Dissipation     | PD               | 350                           | mW       |

| Operating Temperature | T <sub>opr</sub> | <b>- 40∼85</b>                | °C       |

| Storage Temperature   | T <sub>stg</sub> | - 65~150                      | °C       |

# **ELECTRICAL CHARACTERISTICS**

Recommended operating conditions (Unless otherwise specified,  $V_{DD} = 5.0V$ , Ta = 25°C)

| CHARA                  | CTERISTIC            | SYMBOL           | TEST<br>CIR-<br>CUIT | TEST CONDITION            | MIN.                | TYP. | MAX.                | UNIT     |

|------------------------|----------------------|------------------|----------------------|---------------------------|---------------------|------|---------------------|----------|

| Operating :<br>Voltage | Supply               | V <sub>DD</sub>  | _                    | Ta = −40~85°C             | 4.5                 | _    | 5.5                 | ٧        |

| Oscillation            | Scillation Frequency |                  | _                    | _                         | 400                 | _    | 800                 | kHz      |

|                        | "H" Level            | V <sub>IH1</sub> | _                    | (Except RST, RX IN)       | $V_{DD} \times 0.7$ | _    | $V_{DD}$            | <b>V</b> |

| Input                  | "H" Level            | V <sub>IH2</sub> | _                    | (RST, R <sub>X IN</sub> ) | $V_{DD} \times 0.8$ | _    | $V_{DD}$            | ٧        |

| Voltage                | "L" Level            | V <sub>IL1</sub> | _                    | (Except RST, RX IN)       | 0                   | _    | $V_{DD} \times 0.3$ | >        |

|                        | "L" Level            | V <sub>IL2</sub> |                      | (RST, R <sub>X IN</sub> ) | 0                   | _    | $V_{DD} \times 0.2$ | >        |

# DC characteristics (Unless otherwise specified, $V_{DD} = 5.0V$ , Ta = 25°C)

| CHARAC                      | CTERISTIC | SYMBOL         | TEST<br>CIR-<br>CUIT | TEST CONDITION                          | MIN.  | TYP.  | MAX. | UNIT    |

|-----------------------------|-----------|----------------|----------------------|-----------------------------------------|-------|-------|------|---------|

| Operating Supply<br>Current |           | lDD            | _                    | f <sub>osc</sub> = 455kHz               |       | 1.0   | 3.0  | mA      |

| Pull-down Resistor          |           | R <sub>D</sub> |                      | (IN26, C <sub>IN</sub> )                | 100   | 200   | 400  | kΩ      |

| Pull-up Resi                | stor      | RU             | _                    | (RST)                                   | 25    | 50    | 100  | kΩ      |

| Output                      | "H" Level | IOH            | _                    | (CP, HP, DP) V <sub>OH</sub> = 4V       | - 1.0 | - 4.0 | _    | mA      |

| Current                     | "L" Level | lOL            | _                    | (CP, HP, DP) V <sub>OL</sub> = 1V       | 1.0   | 8.0   | _    | mA      |

| Input Leak                  | Current   | ILI            | _                    | V <sub>IN</sub> = V <sub>DD</sub> , GND | - 1.0 | _     | 1.0  | $\mu$ A |

#### **APPLICATION CIRCUIT**

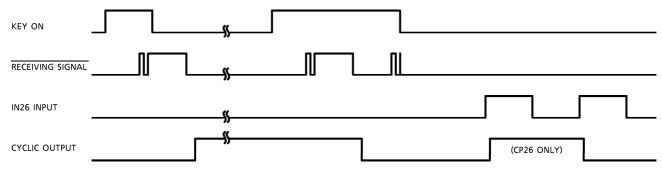

1. Receiver circuit example

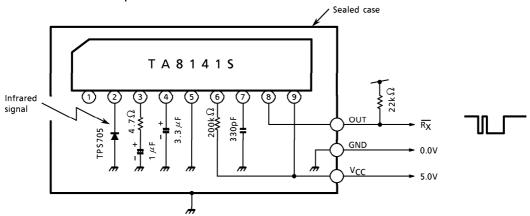

# 2. TC9285P circuit example

(\*) Ceramic oscillator CSB455E (Murata Seisakusyo)  $C_1 = C_2 = 100 \text{pF}$ ,  $R_2 = \text{unnecessary}$  In case of influenced by oscillation noise, add resistor  $R_1$  to  $10 \text{k}\Omega$  MAX. FCR455K3 (TDK)  $C_1 = C_2 = 220 \text{pF}$ ,  $R_2 = 4.7 \text{k}\Omega$ ,  $R_1 = \text{unnecessary}$  In case of influenced by oscillation noise, add resistor  $R_2$  to large (>4.7 k $\Omega$ ). or equivalent

## OUTLINE DRAWING DIP20-P-300-2.54A

Unit: mm

Weight: 1.4g (Typ.)