## **EXTEND CURRENT TRANSFORMER RANGE**

## by PHILIP C. TODD

Transformers are used extensively for current sensing because they can monitor currents with very low power loss and they have wide bandwidth for good waveform fidelity. Current transformers perform well in applications with symmetrical AC currents such as push-pull or full bridge converter topologies. In single-ended applications, especially boost converters, problems can arise because of the need to accurately reproduce high duty factor, unipolar, waveforms. Unipolar pulses may saturate the current transformer and, if this happens, over current protection will be lost and, for current mode control, regulation will be lost and an over voltage condition will result.

The transformer core must be reset after each pulse so that the full range of the transformer will be available for the next pulse. Self reset of the current transformer is the most common techniques used but it has drawbacks. Self reset uses the energy stored in the current transformer core for reset and depends on the open circuit impedance of the current transformer to generate enough volt-seconds in a short period of time for reset. Current transformers operated above a 50% duty factor may not have enough stored energy to allow complete reset in the time available and this situation becomes worse as the duty factor approaches 100%.

The magnetizing inductance of the current transformer must be kept high because this determines the amount of droop the current waveform will exhibit over the pulse period. The higher the inductance the lower the droop will be. The waveform droop opposes slope compensation and should be kept to a minimum. High magnetizing inductance also means that the core stores very little energy which can be used to reset the core.

The current transformer turns ratio generally needs to be high to lower the power loss. The more turns put on the core, however, the greater the leakage inductance and the greater the parallel capacitance. The leakage inductance by itself is generated.

ally not a problem but it will limit the current rise and fall times. The parallel capacitance also limits the bandwidth of the current transformer but it is a greater problem during transformer reset. For the transformer to reset properly, all of the energy stored in the core must be removed. In self reset this energy must transfer from the magnetizing inductance to the parallel capacitance in a resonant manner. If the capacitance is too large, the resonant frequency will be too low and the magnetizing inductance will not be reset before the next pulse begins.

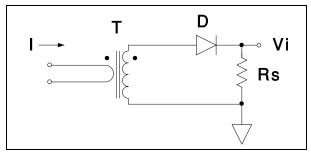

Figure 1: Conventional self-reset current transformer

Figure 1 shows a conventional current transformer circuit which uses self reset. The current I flowing in the primary, causes a current to flow through D and Rs to generate an output voltage proportional to Vc=IRs/N where N is the current transformer turns ratio. The problems discussed above occur during the reset interval when I=O. The core of T may not have enough energy to fully reset itself in the time available given the secondary capacitance of T plus the capacitance of D.

The problems with self reset of current transformers for unipolar pulse applications can be overcome with simple forced reset techniques derived from magnetic amplifiers. Duty factors above 90% are achievable with these techniques.

Design Note DN-41

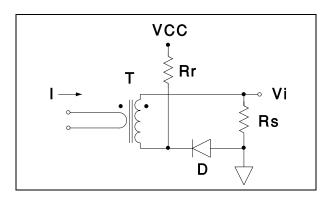

Figure 2: Current transformer with forced reset

Figure 2. shows the same circuit as Figure 1 configured for forced reset. The diode D has been moved from the high side of the transformer secondary winding to the ground side. This, of course, has no effect on the operation of the circuit and during the pulse this circuit behaves exactly as expected. During reset, however, Rr makes the circuit operation quite a bit different.

A current from Vcc through Rr can be much greater than the self reset current available from the magnetizing current of the transformer. This forcing current rapidly charges the parasitic capacitances and reverses the voltage on the secondary of the transformer. The applied volt-seconds can quickly reset the core so that high duty-factor operation is possible.

The forced reset may be high enough to drive the current transformer into saturation and this is an acceptable practice because the core will be saturated in the opposite direction (i.e. full reset) from

the current pulse to be measured. This can be beneficial in some applications as it doubles the number of volt-seconds available from the transformer.

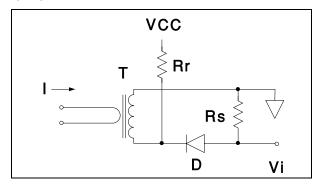

Figure 3: Negative output current sense

In some applications it may be desirable to generate a negative voltage from the current transformer. This can be accomplished without a negative voltage source to reset the transformer. Figure 3 shows the configuration. In this circuit there will be an error because the reset current subtracts from the sense current in Rs during the pulse. Care must be taken to minimize this effect.

There are other circuit configurations which are possible to force reset of the current transformer. Switches may be used to switch the reset current on and off. Additional windings or center tapped windings may be used also. Many circuits are possible and may provide a specific improvement at the expense of complexity. The circuits shown here are the simplest available and illustrate the basic concept.

## **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated